Процессор (ПР) является основным устройством вычислительных машин и систем. Важную роль при изучении ПР играет проведение обучающимися экспериментальных исследований процессоров реальных или абстрактных учебных ЭВМ. Для таких исследований широко применяются программные модели ЭВМ. В качестве средств программного моделирования ПР и ЭВМ используются универсальные среды (например, Delphi и C++) [1–3] и специализированные системы [4]. Во многих случаях использование модели абстрактной учебной ЭВМ имеет преимущества: позволяет разработать ее архитектуру в соответствии с целями обучения на данном этапе, при необходимости объединяя архитектурные решения нескольких реальных процессоров (ЭВМ). При этом такая модель позволяет игнорировать те аспекты в работе ЭВМ, которые на данном уровне рассмотрения не являются существенными [1].

Цель исследования – развитие технологии построения и применения функциональных моделей микропрограммируемых вычислительных структур в учебном процессе, использующей в качестве средства моделирования табличный процессор Microsoft Excel и позволяющей создавать и экспериментально исследовать модели учебных процессоров ЭВМ.

Предлагается подход, основанный на переходе от поразрядного к пословному моделированию основных узлов и блоков процессора с помощью стандартных функций Excel, когда в ячейках могут находиться многоразрядные двоичные коды, а вычисления производятся в десятичной системе счисления. При этом сохраняется представление состояний входов и выходов узлов и блоков на экранных формах в двоичной системе счисления. Такой подход в отличие от применяемого ранее поразрядного моделирования работы узлов и блоков в двоичной системе счисления [5] позволяет значительно уменьшить объем работы по моделированию ПР за счет сокращения числа и сложности формул, требует меньшего количества ячеек Excel. Например, при поразрядном «двоичном» моделировании восьмиразрядной схемы инкремента требуется восемь ячеек памяти и восемь логических функций Excel. При моделировании данной схемы с помощью функций, выполняющих вычисления в десятичной системе счисления, достаточно одной ячейки и трех функций Excel (перевод из двоичной системы счисления в десятичную, добавление к десятичному числу единицы, перевод из десятичной системы счисления в двоичную). Предлагаемый подход позволяет перейти к моделированию более сложных устройств, сохраняя при этом возможность размещения структуры устройства на экранной форме.

Реализация функций основных узлов и блоков с помощью функций Microsoft Excel

В процессе разработки функциональной модели ПР использовались следующие функции Microsoft Excel.

ДВ.В.ДЕС(число). Преобразует двоичное число в десятичное. Пример: =ДВ.В.ДЕС(00001010); =10.

ОСНОВАНИЕ(число;основание;[минимальная_длина]). Преобразует число в текстовое представление с указанным основанием системы счисления. Пример: =ОСНОВАНИЕ(10;2;8); =00001010.

ВЫБОР(номер_индекса;значение1;[значение2];...). При моделировании мультиплексора номер индекса соответствует управляющему входу, выбираемые значения – информационным входам. Поскольку нумерация информационных входов мультиплексора начинается с нуля, а значения номера индекса функции – с единицы, то значение номера индекса функции необходимо увеличивать на единицу. Пример описания работы 8-входового двоичного мультиплексора: =ВЫБОР(ДВ.В.ДЕС(K17)+1;O22;V23;V24;V25;O26;S27;S28;S29), где K17 – трехразрядный двоичный код на управляющем входе мультиплексора, O22, V23, V24, V25, O26, S27, S28, S29 – состояния информационных входов мультиплексора.

ЕСЛИ(лог_выражение; значение_если_истина; [значение_если_ложь]). При моделировании двухвходового (многоразрядного) мультиплексора управляющему входу соответствует первый аргумент функции, нулевому информационному входу – второй, а первому информационному – третий. Пример: =ЕСЛИ(H17=1;D10;D21). Функция также позволяет вычислить значение логической функции сумма по модулю два: =ЕСЛИ(H17=K26;0;1); =H17⊕K26.

ВПР(искомое_значение, таблица, номер_столбца, [интервальный_просмотр]). Функция позволяет моделировать чтение из памяти. Память представляется в виде таблицы, состоящей из двух столбцов. Первый столбец таблицы (столбец адресов) используется для указания последовательности адресов ячеек памяти, а второй (столбец ячеек) состоит из соответствующих этим адресам ячеек памяти. Первый аргумент функции ВПР задает адрес ячейки памяти, из которой необходимо произвести чтение (поиск заданного адреса будет производиться в первом столбце таблицы). Второй аргумент функции ВПР определяет диапазон ячеек таблицы, включающий столбец адресов и столбец ячеек памяти. В третьем столбце указывается номер столбца (столбца ячеек), содержащего считываемую ячейку памяти, адрес которой совпадает с заданным. Четвертый аргумент функции ВПР не используется.

Пример: =ВПР(Z6;'ПР-В'!AB5:AC68;2). Функция выполняет считывание из памяти по адресу, двоичный код которого находится в регистре адреса (Z6), таблица памяти расположена на другом листе Excel (ПР-В) и занимает диапазон AB5:AC68. При вычислении функции ВПР в столбце адресов производится поиск двоичного кода, совпадающего с кодом, заданным в регистре адреса. Результатом вычисления функции ВПР является содержимое ячейки памяти из столбца ячеек (имеющего номер 2), адрес которой совпал с заданным.

Таблица 1

Выполнение микроопераций и формирование признаков с помощью функций Microsoft Excel

|

Микрооперация |

Формула Microsoft Excel |

|

x&y |

AC25: =ОСНОВАНИЕ(БИТ.И(ДВ.В.ДЕС(AA23);ДВ.В.ДЕС(AD23));2;8) |

|

x∨y |

AC25: =ОСНОВАНИЕ(БИТ.ИЛИ(ДВ.В.ДЕС(AA23);ДВ.В.ДЕС(AD23));2;8) |

|

x⊕y |

AC25: =ОСНОВАНИЕ(БИТ.ИСКЛИЛИ(ДВ.В.ДЕС(AA23);ДВ.В.ДЕС(AD23));2;8) |

|

2y.0 |

AC25: =ОСНОВАНИЕ(БИТ.СДВИГЛ(ДВ.В.ДЕС(AD23);1);2;8) |

|

0.y/2 |

AC25: =ОСНОВАНИЕ(БИТ.СДВИГЛ(ДВ.В.ДЕС(AD23);-1);2;8) |

|

x-y-с0 |

AC25: =ЕСЛИ(ЗНАК(СУММ(ДВ.В.ДЕС(AA23);-ДВ.В.ДЕС(AD23);-AE24))=-1; ОСНОВАНИЕ(БИТ.ИЛИ(-СУММ(ДВ.В.ДЕС(AA23);-ДВ.В.ДЕС(AD23);-AE24);128);2;8);ОСНОВАНИЕ(СУММ(ДВ.В.ДЕС(AA23);-ДВ.В.ДЕС(AD23);-AE24);2;8))* |

|

x+y+с0 |

AC25: =ОСНОВАНИЕ(СУММ(ДВ.В.ДЕС(AA23);ДВ.В.ДЕС(AD23);AE24);2;8)) |

|

s |

V23: =ЕСЛИ(P17=0;ЧЗНАЧ(ЛЕВСИМВ(AC25;1));V23) |

|

z |

V24: =ЕСЛИ(P17=0;ЕСЛИ(AC25=»00000000»;1;0);V24) |

|

p |

V25: =ЕСЛИ(P17=0;ЕСЛИ(ИЛИ(И(N17=100;БИТ.СДВИГЛ(ДВ.В.ДЕС(AD23);1)>255);И(N17=110;СУММ(ДВ.В.ДЕС(AA23);-ДВ.В.ДЕС(AD23);-AE24)<-255);И(N17=111;СУММ(ДВ.В.ДЕС(AA23);ДВ.В.ДЕС(AD23);AE24)>255));1;0);V25) (При отрицательном результате вычитания, выполняемого в десятичной системе счисления, с помощью логической функции ИЛИ и десятичного числа 128 в знаковый разряд двоичного кода результата записывается единица) |

Выполнение микроопераций над 8-разрядными двоичными кодами и формирование признаков с помощью функций Excel, выполняющих вычисления в десятичной системе счисления, показано в табл. 1, где x и y – двоичные коды исходных операндов, находящиеся в ячейках AA23 и AD23 соответственно, c0 – значение переноса (заема), поступающее из ячейки AE24 при суммировании (вычитании) операндов в младший разряд, а s, z, p – признаки знака, нуля и переполнения, формируемые при неизменных операндах (P17 = 0).

Разработка функциональной модели процессора с запоминающим устройством

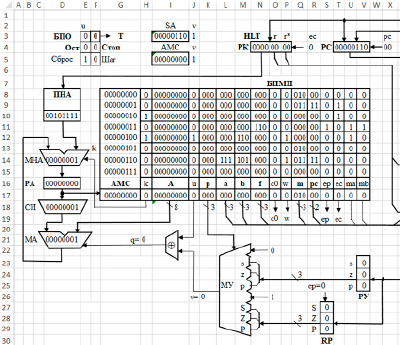

Разработка учебного ПР с микропрограммируемой архитектурой осуществляется на основе восьмиразрядного микропрограммируемого вычислительного устройства, содержащего операционное устройство с общими регистрами и устройство управления с программируемой логикой [5]. Для хранения программ, исходных данных и записи результатов к ПР подключается оперативное запоминающее устройство. Структура процессора с запоминающим устройством отображается на экранной форме ПР-Ф при проведении исследований (рис. 1).

Процессор включает (рис. 1): БПО – блок пуска-останова, РК – регистр команд, PC – программный счетчик, БППД – блок памяти программ и данных; RA – регистр адреса БППД, ПНА – преобразователь начального адреса, БПМП – блок памяти микропрограмм, МНА – мультиплексор начального адреса, РА – регистр адреса, СИ – схему инкремента, МА – мультиплексор адреса, «» – инвертор кода условия, МУ – мультиплексор условий и признаков, РУ – регистр условий, RP – регистр признаков, МД – мультиплексор данных, БР – блок регистров, Mc, Md – мультиплексоры номеров регистров БР; БАЛ – блок арифметико-логический; RB – буферный регистр, ДБР – пультовый дублер блока регистров. Рассмотрим разработку функциональной модели ПР более подробно.

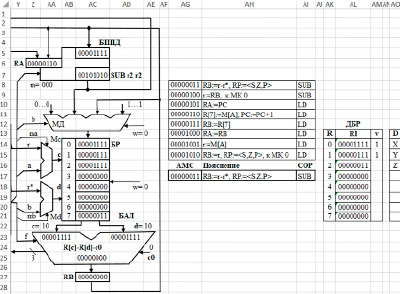

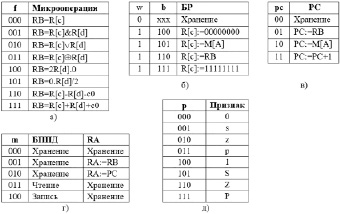

Операционная часть ПР. Основу операционной части процессора составляют БР и БАЛ. БАЛ представляет собой комбинационную схему, выполняющую восемь микроопераций и формирующую значения трех логических условий. Операнды на входы БАЛ поступают из регистров БР, результат записывается в буферный регистр RB. Формируемые БАЛ значения логических условий фиксируются в регистре условий РУ, а при наличии управляющего ep = 1 сохраняются в регистре признаков RP для использования командами условных переходов. Реализация микроопераций и формирование признаков в БАЛ с помощью функций Excel показаны в табл. 1, а используемые для задания микроопераций значения поля микрокоманды f (N17) на рис. 2, а.

а)

б)

Рис. 1. Экранная форма ПР-Ф: левая часть (а) и правая часть (б)

Рис. 2. Значения кодов многоразрядных полей микрокоманды: микроопераций – f (а), БР – w, b (б), РС – pc (в), БППД и RA – m (г), признаков – p (д)

На экранной форме ПР-Ф (рис. 1, б) отображаются поступающие на входы БАЛ (AA23, AD23) операнды из регистров БР и номера этих регистров (AA22, AE22), а также результат выполняемой микрооперации (AC27). Кроме того, в БАЛ выводится условное обозначение выполняемой микрооперации, определяемое по ее коду (N17) с помощью функции Excel: AC25: =ЕСЛИ (P17=0;ВЫБОР(ДВ.В.ДЕС(N17)+1;» R[c]»; »R[c]&R[d]»;»R[c]vR[d]»;«R[c](+mod2) R[d]»;»2R[d].0»;»0.R[d]/2»;»R[c]-R[d]-с0»;»R[c]+R[d]+с0»);» «).

Состояние буферного регистра RB остается неизменным в следующих случаях: производится запись (P17=1) в БР, содержимое RB пересылается в RA БППД или PC, записывается в БППД по адресу, ранее переданному в RA. В остальных случаях в RB заносится результат микрооперации, выполненной в БАЛ. Работа RB описывается формулой

AC27: =ЕСЛИ(ИЛИ(P17=1;ДВ.В.ДЕС ($Q$17)=1;ДВ.В.ДЕС($Q$17)=4;ДВ.В.ДЕС($R$17)=1);AC27;AC25).

Блок регистров состоит из восьми восьмиразрядных регистров, каждый из которых выбирается по номеру, поступающему на адресный вход БР c или d: R[c], R[d]. При этом во время чтения из БР содержимое регистра, номер которого указан на адресном входе с, поступает на левый (AA23), а содержимое регистра, номер которого указан на адресном входе d, – на правый (AD23) вход БАЛ. Номер регистра может быть задан не только в микрокоманде (трехразрядные коды полей a и b, поступающие из БПМП), но и в команде (двухразрядные коды полей r и r*, поступающие из РК). Выбор источника номера регистра определяется разрядами микрокоманды ma и mb и осуществляется мультиплексорами Mc (с=a при ma=0 и с=0r при ma=1) и Md (d=b при mb=0 и d=0r* при mb=1).

Чтение содержимого регистров из БР выполняется с помощью формул

AA23: =ВЫБОР(ДВ.В.ДЕС(ЕСЛИ(U17=0;L17;O4))+1;AC14;AC15;AC16;AC17;AC18;AC19;AC20;AC21),

AD23: =ВЫБОР(ДВ.В.ДЕС(ЕСЛИ(V17=0;M17;P4))+1;AC14;AC15;AC16;AC17;AC18;AC19;AC20;AC21).

Запись в БР производится при поступлении управляющего сигнала w = 1. Номер регистра, в который осуществляется запись, задается на адресном входе с. Источник записываемого кода определяется МД. Сочетания управляющих сигналов и источники кодов при записи в регистр БР показаны на рис. 2, б, где M[A] – содержимое ячейки памяти с адресом A. В БР также предусмотрена возможность специальной записи в пультовом режиме. В этом случае записываемые данные вводятся с клавиатуры в регистры пультового дублера блока регистров ДБР и в поля управляющего сигнала ввода v тех регистров, содержимое которых необходимо занести в соответствующие им регистры БР записываются единицы. При нажатии клавиши «Такт» (F9) данные из регистров ДБР переносятся в регистры БР. Непосредственная запись данных в регистры БР упрощает отладку микропрограмм и программ.

Запись в БР (на примере нулевого регистра) выполняется в соответствии с формулой AC15: =ЕСЛИ(И($E$3=0;AM15=1);AL15;ЕСЛИ(И(P$17=1;ИЛИ(И(U$17=0;ДВ.В.ДЕС($L$17)=$AB15);И(U$17=1;ДВ.В.ДЕС($O$4)=$AB15)));ВЫБОР(ДВ.В.ДЕС ($M$17)-3;»00000000»;$AC$7;$AC$27;»11111111»);AC15)).

В процессе записи в БР на экранной форме ПР-Ф (рис. 1, б) в мультиплексоре данных (МД) отображается условное обозначение выбранных для записи данных, определяемое по формуле: AC12: =ЕСЛИ (P$17=1; ЕСЛИ(V17=0;ВЫБОР(ДВ.В.ДЕС($M$17)-3;»R[c]:=000...0»; «R[c]:=M[A]»;»R[c]:=РБ»;»R[c]:=111...1»);»R[c]:=M[A]»);» «).

К операционной части процессора также относятся регистр команд РК и программный счетчик PC. Регистр команд разделен на три поля: кода операции (COP) и регистров r и r*. Команда считывается из БППД и заносится в РК по сигналу (T17) записи в регистр ec=1. Этот процесс описывается тремя формулами: N4: =ЕСЛИ(T17=1; ЛЕВСИМВ(AC7;4);N4); O4: =ЕСЛИ(T17=1; ПСТР(AC7;5;2);O4); P4: =ЕСЛИ(T17=1;ПСТР (AC7;7;2);P4). Над полем кода операции РК на экранной форме ПР-Ф (рис. 1, а) отображается символическое обозначение кода операции, считываемое из таблицы преобразователя начального адреса ПНА, расположенной на листе ввода данных ПР-В и содержащей три столбца: код операции, адрес первой микрокоманды микропрограммы операции и символическое обозначение кода операции. Символическое обозначение кода операции считывается с помощью формулы: M3: =ВПР(N4;’ПР-В’!B5:D20;3) из дополнительного третьего столбца таблицы.

Программный счетчик имеет четыре режима работы, задаваемые с помощью поля микрокоманды pc (R17) (рис. 2, в). Кроме того, по сигналу «Сброс» в PC может быть занесен предварительно набранный на клавиатуре стартовый адрес SA (I3). Работа PC описывается следующей формулой: T4: =ЕСЛИ(И(E3=0;J3=1);I3;ВЫБОР(ДЕС(R17;2)+1;T4;AC27;AC7; ЕСЛИ(F3=0;ОСНОВАНИЕ(ДЕС(T4;2)+1;2;8);T4))).

Управляющая часть ПР. Управляющая часть процессора представляет собой устройство управления с программируемой логикой, в БПМП которого в виде двоичного кода микропрограммы хранится алгоритм работы ПР. Считываемая из БПМП микрокоманда обеспечивает выдачу управляющих сигналов для операционной части ПР и запоминающего устройства, а также формирование адреса следующей микрокоманды с учетом значений логических условий. Микрокоманда содержит 15 полей. В табл. 2 в соответствии с форматом микрокоманды приведены: обозначение (адрес ячейки Excel), разрядность и назначение каждого поля.

Таблица 2

Поля микрокоманды

|

Поле (ячейка) |

Разряд-ность |

Назначение |

|

k (H17) |

1 |

Занесение в РА микрокоманды адреса из ПНА (при k=1) |

|

A (I17) |

8 |

Адрес следующей микрокоманды |

|

u (J17) |

1 |

Инверсия значения выбранного условия (признака) (при u=1) |

|

p (K17) |

3 |

Код выбираемого условия (признака) |

|

a (L17) |

3 |

Номер регистра в БР (при чтении подается на левый вход БАЛ) |

|

b (M17) |

3 |

Номер регистра в БР (при чтении подается на правый вход БАЛ) |

|

f (N17) |

3 |

Код микрооперации, выполняемой в БАЛ |

|

с0 (O17) |

1 |

Значение входа переноса в младший разряд БАЛ |

|

w (P17) |

1 |

Запись в БР (при w=1) |

|

m (Q17) |

3 |

Код микрооперации, выполняемой в БППД и РА |

|

pc (R17) |

2 |

Код микрооперации, выполняемой в РС |

|

ep (S17) |

1 |

Запись в регистр признаков RP (при ep=1) |

|

ec (T17) |

1 |

Запись в регистр команд РК (при ec=1) |

|

ma (U17) |

1 |

Выбор источника номера регистра (с=a при ma=0 и с=0r при ma=1) |

|

mb (V17) |

1 |

Выбор источника номера регистра (d=b при mb=0 и d=0r* при mb=1) |

Значения кодов многоразрядных полей микрокоманды p, f, m и pc приведены на рис. 2.

БПМП отображается на экранной форме проведения исследований ПР-Ф в виде блока памяти, в котором выделено окно микрокоманд, содержащее восемь последовательно расположенных 33-разрядных ячеек памяти (рис. 1, а). Слева от ячеек выводятся их адреса. Адрес верхней ячейки памяти задается регистром РА БПМП. Микрокоманда из этой ячейки поступает на выход БПМП и отображается в нижней части БПМП, располагаясь после условных обозначений полей. Каждая запись в РА нового адреса микрокоманды приводит к обновлению содержимого окна микрокоманд: в окне отображаются восемь микрокоманд, расположенных в последовательных ячейках, начиная с адреса в РА. Окно микрокоманд имеет продолжение, отображаемое в правой части экранной формы ПР-Ф (рис. 1, б). В этом продолжении окна повторяется адрес микрокоманды и выводятся дополнительные сведения о микрокоманде: выполняемые микрооперации (поле Пояснение) и код операции, для выполнения которой используется микрокоманда (поле COP).

По сигналу «Сброс» в РА (D16) может быть занесен предварительно набранный на клавиатуре адрес микрокоманды АМК (I5), с которой начнется выполнение микропрограммы. В качестве источников адреса следующей МК для РА выступают: ПНА (D10) (обеспечивается МНА при k=1); СИ (D18) (обеспечивается МНА при k=0 и МА при q=0); БПМП – поле адреса перехода А из микрокоманды (обеспечивается МНА при k=0 и МА при q=1).

Начальный адрес микропрограммы операции считывается из таблицы, моделирующей работу ПНА, которая расположена на листе ввода данных ПР-В и содержит три столбца: код операции, адрес первой микрокоманды микропрограммы операции и символическое обозначение кода операции. Для считывания из ПНА адреса первой микрокоманды микропрограммы операции используется формула: D10: =ВПР(N4;’ПР-В’!B5:C20;2). Увеличение адреса на единицу в СИ реализовано с помощью формулы: D16: =ОСНОВАНИЕ(СУММ(ДВ.В.ДЕС(D16);1);2;8).

Работа PА БПМП описывается следующей формулой: D16: =ЕСЛИ(И(E3=0;J5=1);I5;ЕСЛИ($F3=1;ЕСЛИ($H17=1;D10;ЕСЛИ(ЕСЛИ(J17=ВЫБОР(ДВ.В.ДЕС(K17)+1;O22;V23;V24;V25;O26;S27;S28;S29);0;1);I17;D18));D16)).

Занесение данных в ПНА и БПМП производится на листе ПР-В путем ввода данных с клавиатуры в ячейки таблиц, моделирующих ПНА и БПМП, а также ячейки, предусмотренные для ввода дополнительной информации (пояснения, коды операций).

Блок памяти программ и данных. Работа БППД моделируется с помощью таблицы, расположенной на листе ПР-В. Чтение данных реализуется формулой: AC7: =ВПР(Z6;’ПР-В’!AB5:AC68;2). Одновременно с чтением данных справа от выхода БППД на форме ПР-Ф (рис. 1, б) отображается мнемоническое обозначение содержимого считываемой ячейки памяти, предварительно введенное в дополнительный столбец таблицы. Отображение ячейки дополнительного столбца осуществляется формулой: AD7: =ВПР(Z6;’ПР-В’!AA5:AG68;7).

Процессор записывает данные в ячейку БППД при наличии в коде микрокоманды сигнала записи (m=100) и совпадении адреса ячейки с адресом в RA (Z6). Ввод данных в БППД производится на экранной форме ПР-В аналогично записи в БР с помощью ячеек пультового дублера БППД. Данные подлежащие записи вводятся с клавиатуры в ячейки пультового дублера БППД и в поля управляющего сигнала ввода v тех ячеек, содержимое которых необходимо занести в соответствующие им ячейки БППД записываются единицы. При нажатии клавиши «Такт» (F9) данные из ячеек дублера БППД переносятся в ячейки БППД. Запись данных в БППД (на примере нулевой ячейки памяти) производится с помощью формулы: AB5: =ЕСЛИ(AE5=1;AD5;ЕСЛИ(И(ДЕС(‘ПР-Ф6’!Q$17;2)=4;’ПР-Ф6’!Z$6=’ПР-В’!AA5);’ПР-Ф6’!AC$27;AB5)).

Функционирование процессора. Моделируется работа ПР под действием сигналов, вырабатываемых блоком пуска-останова БПО (рис. 1, а), в состав которого входит генератор тактовых импульсов (ГТИ). В БПО с клавиатуры подаются сигналы «Сброс» (E5) и «Шаг» (F5) (в соответствующую ячейку Excel вводится необходимое значение сигнала (0 или 1) и нажимается клавиша F9). По сигналу «Сброс» в БПО производятся начальные установки регистров процессора и подготовка ГТИ к работе. По сигналу «Шаг» процессор переходит в покомандный режим работы. В БПО вырабатываются два признака «Ост» (E4) и «Стоп» (F4). Признак «Ост» (останов) принимает единичное значение, если выполняется микрокоманда, содержащая микрооперацию останова (p=100) и нулевое значение – по сигналу «Сброс»: E4: =ЕСЛИ(E5=1;0;ЕСЛИ(K17=»100»;1;E4)). Признак «Стоп» принимает единичное значение, если единичное значение имеет сигнал «Шаг» и выполняется микрокоманда, содержащая микрооперацию k перехода по коду операции, и нулевое значение – по сигналу «Сброс»: F4: =ЕСЛИ(И(F5=1;H17=1);1;ЕСЛИ(E5=1;0;F4)).

Используется известная модель ГТИ на основе T триггера: T(t+1)=u(τ⊕T(t)), где T(t) – состояние триггера до подачи сигнала τ, формируемого при нажатии клавиши F9, а T(t+1) – после подачи этого сигнала, u – состояние управляющего входа (при u=0 состояние выхода T(t+1) генератора принимает нулевое значение и сохраняет его при нажатиях клавиши F9) [5]. Логическая формула Т триггера представляется следующей формулой Excel: F3: =ЕСЛИ(И(E3;НЕ(F3));1;0). Управляющий вход ГТИ принимает нулевое значение, останавливающее работу генератора, когда единичное значение имеет сигнал «Сброс» или признаки: «Ост» или «Стоп»: E3: =ЕСЛИ(ИЛИ(E5=1;E4=1;F4=1);0;1).

Проведению экспериментальных исследований предшествует изменение параметров Microsoft Excel, связанных с вычислением формул (выбираются вычисления в книге «вручную» и включаются итеративные вычисления с предельным числом итераций). БПО обеспечивает работу процессора в следующих режимах.

1. Выполнение микрокоманд по полутактам. Подается сигнал «Сброс» в параметрах Microsoft Excel, связанных с вычислением формул, выбираются вычисления в книге «вручную» и включаются итеративные вычисления с предельным числом итераций равным единице. При данных настройках параметров Microsoft Excel микрокоманда выполняется за два полутакта, каждый из которых требует нажатия клавиши F9.

В первом полутакте при T=1 нажатие клавиши F9 вызывает считывание очередной МК из БПМП по адресу из РА и выполнение заданных в операционной части МК преобразований. В первом полутакте либо выбираются операнды из БР и выполняется заданная микрооперация в БАЛ с фиксацией полученного результата в буферном регистре RB, а значений признаков в соответствующих триггерах признаков, либо производится запись в заданный регистр БР операнда, выбранного из одного из четырех источников МД.

Во втором полутакте при T=0 нажатие клавиши F9 вызывает выполнение преобразований по формированию в РА адреса следующий МК. Преобразования задаются в управляющей части текущей МК, считанной в предыдущем полутакте. При этом условный переход по адресу, указанному в управляющей части текущей МК, осуществляется в соответствии со значениями признаков, сформированными и запомненными в предыдущем полутакте.

2. Выполнение микрокоманд по тактам. Для того чтобы МК выполнялась в ПР при однократном нажатии клавиши F9, необходимо в параметрах Microsoft Excel, связанных с вычислением формул, включить итеративные вычисления с предельным числом итераций равным двум.

3. Выполнение программы. Для того чтобы программа выполнялась в ПР при однократном нажатии клавиши F9, необходимо в параметрах Microsoft Excel, связанных с вычислением формул, включить итеративные вычисления с предельным числом итераций, превышающим удвоенное число микрокоманд, выполняющихся при выполнении программы.

4. Выполнение программы по командам. Для того чтобы программа выполнялась в ПР при однократном нажатии клавиши F9 по командам, необходимо записать единицу в ячейку F5, соответствующую режиму «Шаг», и в параметрах Microsoft Excel, связанных с вычислением формул, включить итеративные вычисления с предельным числом итераций, превышающим удвоенное максимальное число микрокоманд, выполняющихся при выполнении команды.

Заключение

Созданная функциональная модель учебного процессора с микропрограммируемой архитектурой позволяет производить разработку и экспериментальное исследование учебных процессоров с различной архитектурой на основе их микропрограммной реализации, используя два уровня управления: микропрограммный и программный. В качестве исходных данных может выступать простая вычислительная задача, на примере программного решения которой будет исследоваться работа процессора. При этом обучающийся, выполняя индивидуальное задание, решает следующие проектные задачи: разработка (выбор) алгоритма решения вычислительной задачи; определение архитектуры ПР и программирование; кодирование программы и распределение памяти программ и данных; разработка микропрограммы командного цикла и составление таблиц прошивок преобразователя начального адреса и блока памяти микропрограмм; ввод и отладка микропрограммы командного цикла и программы решения вычислительной задачи с использованием экранных форм.

Отладка микропрограммы командного цикла осуществляется в режимах выполнения микрокоманд по полутактам и тактам. При этом используется возможность задания в РА БПМ предварительно набранного на клавиатуре адреса микрокоманды АМК, с которой начнется выполнение микропрограммы, а также занесение данных в выбранные регистры БР через регистры пультового дублера БР. Отладка программы решения вычислительной задачи производится в режиме выполнения программы по командам. В процессе отладки используется возможность задания в PC предварительно набранного на клавиатуре адреса команды SA, с которой начнется выполнение программы, а также занесение данных в выбранные ячейки БППД через ячейки пультового дублера БППД.

Использование обучающимися предлагаемой функциональной модели учебного процессора с микропрограммируемой архитектурой позволяет им более глубоко изучить архитектуру, структуру и функционирование ПР. Дальнейшее развитие реализуемого с помощью модели процессора может быть связано с развитием системы команд (например, введением различных способов адресации и организацией обращений к подпрограммам). Рассмотренный подход к построению учебных процессоров, основанный на реализации функций узлов и блоков процессора с помощью функций Microsoft Excel, дает возможность обучающимся не только модифицировать описанную функциональную модель ПР (например, увеличить разрядность и число общих регистров, включить в состав ПР отдельный регистр указателя стека), но и создавать новые функциональные модели ПР.

Библиографическая ссылка

Страбыкин Д.А. ФУНКЦИОНАЛЬНАЯ МОДЕЛЬ УЧЕБНОГО ПРОЦЕССОРА С МИКРОПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ В MICROSOFT EXCEL // Современные наукоемкие технологии. 2023. № 2. С. 102-110;URL: https://top-technologies.ru/ru/article/view?id=39530 (дата обращения: 27.04.2026).

DOI: https://doi.org/10.17513/snt.39530