Неотъемлемой частью процесса обучения основам вычислительной техники является практическая подготовка. Применение в учебном процессе программных продуктов из инструментария разработчиков средств вычислительной техники не всегда оправдано. Коммерческие программы профессионального уровня имеют низкую «обучающую» ценность для большинства учебных заведений, поскольку рассчитаны на использование высококвалифицированными специалистами и имеют высокую рыночную стоимость [1]. Более глубокому усвоению материала при изучении простейших вычислительных устройств способствует разработка и экспериментальное исследование обучающимися программных моделей устройств с использованием адаптированных для учебного процесса программных систем и эмуляторов цифровых автоматов [2–4].

Цель исследования – развитие технологии построения и использования функциональных моделей микропрограммируемых вычислительных устройств (МПВУ) в учебном процессе, основанной на применении табличного процессора Microsoft Excel и позволяющей создавать модели, в которых возможна микропрограммная реализация алгоритмов различных операций путем смены содержимого памяти микропрограмм.

Под МПВУ понимается устройство, способное выполнять алгоритмы, представленные в виде микропрограмм. МПВУ состоит из двух частей: операционной и управляющей. Основу операционной части МПВУ составляют два блока: регистров (БР) и арифметико-логический (БАЛ). При функционально полном наборе микроопераций и логических условий в БАЛ и достаточном числе регистров в БР операционная часть МПВУ позволяет выполнить любой алгоритм в виде микропрограммы.

Основу управляющей части составляют: блок памяти микропрограмм и схемы формирования адреса следующей микрокоманды. Смена содержимого блока памяти микропрограмм дает возможность перенастраивать МПВУ на выполнение новых алгоритмов.

В процессе создания функциональной модели МПВУ используется технология, основанная на применении табличного процессора Microsoft Excel, позволяющего создавать действующие модели без разработки программного кода по принципу «программирование без программирования» [5]. Создание функциональной модели МПВУ имеет следующие особенности. При разработке операционной части МПВУ определяется разрядность и число регистров БР, а также состав микроопераций и логических условий БАЛ, обеспечивающих выполнение микропрограмм операций, включаемых в учебные задания. При разработке управляющей части ВУ определяется формат микрокоманды, способы формирования адреса следующей микрокоманды и объем памяти микропрограмм.

Разработка функциональной модели микропрограммируемого вычислительного устройства

Рассмотрим разработку функциональной модели МПВУ на примере следующего восьмиразрядного устройства.

Операционная часть МПВУ. Операционная часть МПВУ включает БР из восьми восьмиразрядных регистров и комбинационный БАЛ, который выполняет восемь микроопераций и формирует значения трех логических условий.

Два трехразрядных адресных входа БР a и b позволяют одновременно выбирать в БР пару регистров, содержимое которых поступает по двум магистралям на входы БАЛ. При этом содержимое регистра, выбранное с помощью адреса a, поступает на вход А, а содержимое регистра, выбранное с помощью адреса b, – на вход B БАЛ. В течение такта в БАЛ над данными, поступающими на входы A и B, выполняется одна из восьми микроопераций и формируются значения логических условий. Результат микрооперации записывается в буферный регистр результата РБ, а значения логических условий передаются в управляющую часть МПВУ. Содержимое регистра РБ может быть записано в любой регистр БР, адрес которого задается на адресном входе b.

Описание выполняемых БАЛ микроопераций с помощью логических функций и представление их в виде логических функций табличного процессора Microsoft Excel содержится в работе [5]. Набор микроопераций, выполняемых БАЛ, приведен в табл. 1, где f – код микрооперации; R[a] – содержимое регистра БР с адресом a; R[b] – содержимое регистра БР с адресом b; РБ – содержимое буферного регистра результата микрооперации.

В БАЛ на основании полученного результата микрооперации формируются следующие логические условия: s – старший разряд; z – равенство результата нулю; p – перенос из старшего разряда.

Запись в БР возможна из входного регистра данных РД и буферного регистра результата РБ. Кроме того, в любой регистр БР может быть записан код «00000000» или «11111111». Набор микроопераций записи в регистры БР из различных источников, определяемый сигналом записи w и двумя младшими разрядами адресного входа a БР, приведен в табл. 2, где символ «x» представляет разряд регистра a, неиспользуемый в данной микрооперации.

Таблица 1

Микрооперации БАЛ

|

f |

Микрооперация |

Пояснение |

|

000 |

РБ = R[a] |

Пересылка (формирование значения признаков) |

|

001 |

РБ = R[a]&R[b] |

Конъюнкция |

|

010 |

РБ = R[a]∨[b] |

Дизъюнкция |

|

011 |

РБ = R[a]⊕R[b] |

Сумма по модулю два |

|

100 |

РБ = 2R[b].с0 |

Сдвиг в сторону старших разрядов с занесением в освобождающийся разряд значения входа переноса с0 |

|

101 |

РБ = p.R[b]/2 |

Сдвиг в сторону младших разрядов с занесением в освобождающийся разряд значения выхода переноса из старшего разряда p |

|

110 |

РБ = R[a]-R[b]-с0 |

Вычитание с вычитанием из результата значения входа переноса c0 |

|

111 |

РБ = R[a]+R[b]+с0 |

Суммирование с добавлением к результату значения входа переноса c0 |

Таблица 2

Микрооперации записи в регистры БР

|

w |

a |

Микрооперация записи в БР |

Пояснение |

|

0 |

xxx |

– |

Хранение информации (состояния регистров БР не изменяются) |

|

1 |

х00 |

R[b]: = 00000000 |

Запись двоичного кода «00…0» в регистр БР с адресом b |

|

1 |

x01 |

R[b]: = РД |

Запись содержимого регистра ввода данных РД в регистр БР с адресом b |

|

1 |

х10 |

R[b]: = РБ |

Запись содержимого буферного регистра РБ в регистр БР с адресом b |

|

1 |

x11 |

R[b]: = 11111111 |

Запись двоичного кода «11…1» в регистр БР с адресом b |

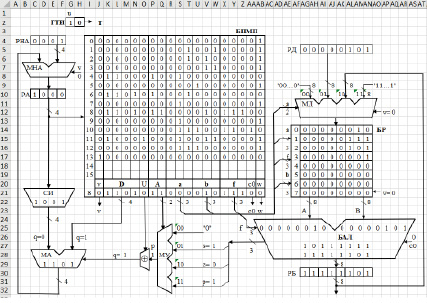

На рис. 1 приведена экранная форма функциональной модели МПВУ, в операционной части которой изображены: БР, БАЛ, буферный регистр РБ, регистр данных РД и мультиплексор данных МД. На экранной форме кроме управляющих сигналов отображаются состояния разрядов всех регистров, а также номера регистров БР. В БАЛ на экран выводятся двоичные коды операндов на входах и результаты выполняемой микрооперации на выходе. Для микрооперации суммирования (вычитания) в БАЛ над результатом также отображается слово переносов (заёмов), младшие разряды которого располагаются слева. Экранная форма обеспечивает непосредственный ввод операнда в РД.

Описание работы БР в режиме чтения содержимого регистра, выбираемого с помощью трехразрядного адресного входа a, рассмотрим на примере младших (нулевых) разрядов регистров R[a]0, a = 0,1,…,7. Значение младшего разряда входа А БАЛ, на который поступает одноименный разряд регистра БР, считываемый с помощью адреса a = a2a1a0, вычисляется по формуле:

A0 = ⅂a2⅂a1⅂a0R[0]0∨⅂a2⅂a1a0R[1]0∨⅂a2a1⅂a0R[2]0∨⅂a2a1a0R[030∨a2⅂a1⅂a0R[4]0∨a2⅂a1a0R[5]0∨a2a1⅂a0R[6]0∨a2a1a0R[7]0,

которой соответствует следующая формула MS Excel.

AI25: = ЕСЛИ(И(НЕ($R21);НЕ($S21);НЕ($T21));AN14;ЕСЛИ(И(НЕ($R21);НЕ($S21);$T21);AN15;ЕСЛИ(И(НЕ($R21);$S21;НЕ($T21));AN16;ЕСЛИ(И(НЕ($R21);$S21;$T21); AN17;ЕСЛИ(И($R21;НЕ($S21);НЕ($T21));AN18;ЕСЛИ(И($R21;НЕ($S21);$T21);AN19;ЕСЛИ(И($R21;$S21;НЕ($T21));AN20;ЕСЛИ(И($R21;$S21;$T21);AN21;» «)))))))).

Описание работы БР в режиме чтения содержимого регистра, выбираемого с помощью трехразрядного адресного входа b, осуществляется аналогично.

Запись в БР рассмотрим на примере записи в младший разряд нулевого регистра. Операнды на входы регистров РБ поступают с выхода мультиплексора данных МД в соответствии с сигналами на двухразрядном управляющем входе мультиплексора, на который поступают два младших разряда адреса a БР: a1a0. Работа МД0 (младшего разряда МД) описывается логической формулой:

МД0 = w(⅂a1⅂a00∨⅂a1a0РД0∨a1⅂a0РБ0a1a01),

где w – сигнал записи в БР, РД0 – нулевой разряд регистра данных РД, а РБ0 – буферного регистра.

Рис. 1. Экранная форма функциональной модели МПВУ, где ГТИ – генератор тактовых импульсов, БПМП – блок памяти микропрограмм, БР – блок регистров, БАЛ – блок арифметико-логический; РНА – регистр начального адреса, МНА – мультиплексор начального адреса РА – регистр адреса, СИ – схема инкремента, МА – мультиплексор адреса, ⊕ – инвертор кода условия, МУ – мультиплексор условий, РД – регистр данных, МД – мультиплексор данных, РБ – регистр буферный.

При моделировании работы МД используется следующая формула MS Excel:

AN12: = ЕСЛИ($AB$21 = 0;» «;ЕСЛИ(И(НЕ($S$21);НЕ($T$21));0;ЕСЛИ(И(НЕ($S$21); $T$21);AN5;ЕСЛИ(И($S$21;НЕ($T$21)); AN30;ЕСЛИ(И($S$21;$T$21);1;» «))))).

Формула позволяет выводить на экран ноль или единицу только в тех случаях, когда есть сигнал записи (w) в БР и используется одно из четырех допустимых сочетаний значений разрядов адреса a1a0, а в остальных случаях отображается пробел.

Запись в нулевой разряд нулевого регистра значения сигнала с выхода мультиплексора данных МД0 описывается логической формулой

R[0]0(t+1) = ⅂b2⅂b1⅂b0wМД0∨⅂(⅂b2⅂b1⅂b0w)R[0]0(t),

где R[0]0(t) – состояние нулевого разряда нулевого регистра в режиме хранения до записи, а R[0]0(t+1) – после записи, b2b1b0 – разряды адресного входа b в БР.

При моделировании работы регистра БР используется следующая формула MS Excel:

= ЕСЛИ(И(НЕ($U$21);НЕ($V$21); НЕ($W$21);$AB$21);AN12;AN14).

Управляющая часть МПВУ. Микрокоманда (МК), состоит из двух частей: управляющей (УЧ) и операционной (ОЧ). Формат МК с указанием условных обозначений и разрядностей всех полей приведен на рис. 2, где D – адрес следующей МК в блоке памяти микропрограмм; U – код инверсии значения выбранного логического условия; A – код выбираемого логического условия; a – адрес (номер) первого выбираемого в БР регистра; b – адрес (номер) второго выбираемого в БР регистра; f – код микрооперации, выполняемой в БАЛ; c0 – вход переноса в БАЛ; w – сигнал записи в данных в регистр БР.

|

УЧ МК |

ОЧ МК |

|||||||

|

v |

D |

U |

A |

a |

b |

f |

c0 |

w |

|

1 |

4 |

1 |

2 |

3 |

3 |

3 |

1 |

1 |

Рис. 2. Формат микрокоманды

Поля операционной части МК используются для управления работой БР и БАЛ, обеспечивая необходимые пересылки операндов и выполнение над ними заданных микроопераций. Поля управляющей части МК определяют порядок формирования адреса в БПМП следующей выполняемой МК в соответствии с реализуемым алгоритмом и с учетом значений логических условий, поступающих из БАЛ.

На экранной форме функциональной модели МПВУ, приведенной на рис. 1, в управляющей части устройства изображены: блок памяти микропрограмм БПМП; регистр начального адреса РНА, мультиплексор начального адреса МНА, регистр адреса РА, схема инкремента СИ, мультиплексор адреса МА, мультиплексор условий МУ с инвертором кода условия «⊕». На экранной форме отображаются состояния разрядов регистров РА и РНА и состояния разрядов используемых ячеек блока памяти, а также состояния входов и выходов комбинационных схем (МУ, «⊕», МА, СИ). Кроме того, в нижней части БПМП выводится считываемая МК и адрес ячейки, в которой она записана. Экранная форма обеспечивает непосредственный ввод двоичных кодов МК в БПМП, а также задание начального адреса МК в РНА.

Описание логическими функциями работы БПМП в режиме чтения и представление их в виде логических функций табличного процессора Microsoft Excel осуществляется аналогично тому, как это делается при моделировании работы РБ в режиме чтения данных.

В каждом такте работы МПВУ из ячейки блока памяти микропрограмм по адресу, указанному в регистре адреса, считывается МК. Операционная часть считанной МК используется для подачи в БР и БАЛ управляющих сигналов, под действием которых выполняются заданные микрооперации, а с помощью управляющей части МК в регистре адреса формируется адрес следующей МК.

На линейных участках микропрограммы следующая для выполнения МК помещается в следующую по порядку ячейку БПМП, поэтому формирование адреса производится с помощью схемы инкремента, которая увеличивает содержимое РА на единицу. Для подключения СИ ко входам РА используется мультиплексор адреса, на управляющий вход которого необходимо подать сигнал q = 0. Подача сигнала q = 0 реализуется путем подачи на управляющий вход A мультиплексора условий кода «00», обеспечивающего передачу на выход сигнала P = 0 (соответствующего тождественно ложному логическому условию). Сигнал на входе q мультиплексора адреса зависит от сигнала на выходе инвертора условий (U): q = P⊕U, при U = 0 формируется необходимое значение сигнала q = 0.

Для реализации переходов в микропрограмме на управляющий вход q мультиплексора адреса подается значение логического условия (или его инверсия), что обеспечивает передачу в регистр адреса либо следующего по порядку адреса с выхода схемы инкремента, либо адреса перехода из поля D управляющей части микрокоманды. Значение управляющего входа мультиплексора адреса определяется следующими формулами:

q = P⊕U, P = ⅂A1⅂A00∨A1⅂A0s∨A1⅂A0z∨A1A0p,

где A1, A0 – разряды поля условия А; «⅂» – символ инверсии переменой. Безусловный переход реализуется при А = 00 и U = 1.

Для перехода на начальный адрес микропрограммы используется адрес, который предварительно помещается в регистр начального адреса РНА. Переход на адрес из РНА осуществляется при задании в МК v = 1.

На экранной форме функциональной модели МПВУ (рис. 1) также отображается генератор тактовых импульсов (ГТИ). При установке на экранной форме управляющего входа ГТИ u в единичное состояние каждое нажатие клавиши F9 («Такт») меняет состояние выхода Т генератора на противоположное. При u = 0 состояние выхода Т генератора принимает нулевое значение и сохраняет его при нажатиях клавиши F9. Работа ГТИ моделируется Т триггером с установкой в «0» и описывается формулой:

T(t+1) = u(t⊕T(t)),

где T(t) – состояние триггера до подачи сигнала t, формируемого при нажатии клавиши F9, а T(t+1) – после подачи этого сигнала. Используемая логическая формула Т триггера представляется следующей формулой MS Excel:

H2: = ЕСЛИ(И(G2;НЕ(H2));1;0).

Проведению экспериментальных исследований предшествует занесение в ячейку G2 единицы и изменение параметров Microsoft Excel, связанных с вычислением формул: выбираются вычисления в книге «вручную» и включаются итеративные вычисления с предельным числом итераций, равным единице.

При данных настройках параметров Microsoft Excel микрокоманда выполняется за два полутакта, каждый из которых требует нажатия клавиши F9. В первом полутакте при T = 1 нажатие клавиши F9 вызывает считывание очередной МК из БПМП по адресу из РА и выполнение заданных в операционной части МК преобразований. В первом полутакте либо выбираются операнды из БР и выполняется заданная микрооперация в БАЛ с фиксацией полученного результата в буферном регистре РБ, а значений признаков в соответствующих триггерах признаков, либо производится запись в заданный регистр БР операнда, выбранного из одного из четырех источников в соответствии с двумя младшими разрядами адресного входа a БР.

Во втором полутакте при T = 0 нажатие клавиши F9 вызывает выполнение преобразований по формированию в РА адреса следующий МК. Преобразования задаются в управляющей части текущей МК, считанной в предыдущем полутакте. При этом условный переход по адресу, указанному в управляющей части текущей МК, осуществляется в соответствии со значениями признаков, сформированными и запомненными в предыдущем полутакте.

Для того чтобы МК выполнялась в МПВУ при однократном нажатии клавиши F9, необходимо в параметрах Microsoft Excel, связанных с вычислением формул, включить итеративные вычисления с предельным числом итераций равным двум.

Применение функциональной модели МПВУ в учебном процессе

Созданная функциональная модель МПВУ позволяет производить разработку и отладку учебных микропрограмм. При этом обучающийся решает задачу микропрограммной реализации заданной операции в МПВУ. В процессе решения задачи выделяются следующие шаги.

1. Выбор алгоритма выполнения операции.

2. Разработка микропрограммы выполнения операции.

3. Кодирование микропрограммы и составление таблицы прошивки для памяти микропрограмм.

4. Занесение таблицы прошивки в блок памяти микропрограмм.

5. Ввод исходных данных и отладка микропрограммы.

Рассмотрим применение МПВУ в учебном процессе на примере операции деления нацело 8-разрядного двоичного числа X на 8-разрядное двоичное число Y.

1. Выбор алгоритма выполнения операции. Для выполнения заданной операции предлагается использовать следующий алгоритм. Если число Y = 0, то деление не выполняется, а формируется признак переполнения P. В противном случае из делимого X вычитается делитель Y, и если разность R положительное число, то частное Z увеличивается на единицу, а разность R выступает в качестве нового уменьшаемого на следующем шаге. Процесс вычитания продолжается до тех пор, пока не будет получена отрицательная разность. В этом случае Z будет представлять собой искомое частное от деления X на Y нацело [5].

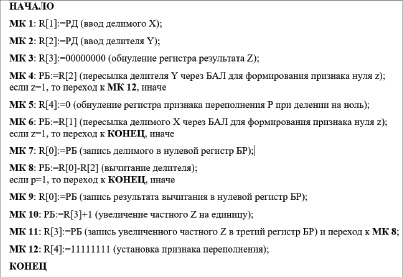

2. Разработка микропрограммы выполнения операции. Микропрограмма разрабатывается на основе алгоритма выполнения операции. В процессе разработки микропрограммы исходным данным, промежуточным и конечным результатам выделяются регистры БР (Х – R[1], Y – R[2], Z – R[3], P – R[4], R – R[0]); выбирается подмножество необходимых для реализации микроопераций (ввода исходных данных, обнуления регистров, пересылки, вычитания, инкремента, записи в регистр кода 11111111) и логических условий (z – равенство результата нулю; p – перенос из старшего разряда). Микропрограмма деления чисел нацело для МПВУ может быть представлена в следующем виде (рис. 3).

3. Кодирование микропрограммы и составление таблицы прошивки для памяти микропрограмм. Для разработанной микропрограммы определяется начальный адрес в БПМП, начиная с которого микропрограмма будет записана в память.

Формируются двоичные коды микрокоманд путем записи в каждое поле МК необходимого двоичного кода, которые помещаются в специальную таблицу прошивки (табл. 3). В рассматриваемом примере кодированная микропрограмма размещается с 1 по 13 ячейки БПМП. При этом неиспользуемые в МК поля имеют двоичные коды, состоящие из нулей.

Рис. 3. Микропрограмма деления чисел нацело

Таблица 3

Таблица прошивки для микропрограммы деления чисел нацело

|

Адрес ЯП |

Управляющая часть МК |

Операционная часть МК |

|||||||||||||||||

|

v |

D |

U |

A |

a |

b |

f |

c0 |

w |

|||||||||||

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|

3 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

|

4 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

5 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

8 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|

9 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

10 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

11 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

|

12 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

13 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

4. Занесение таблицы прошивки в блок памяти микропрограмм. Двоичные коды МК заносятся в БПМП с помощью экранной формы, которая позволяет вводить и редактировать МК, используя возможности Microsoft Excel. Пример занесенной в БПМП таблицы прошивок приведен на рис. 1.

5. Ввод исходных данных и отладка микропрограммы. Запуску функциональной модели МПВУ для ввода данных и отладки микропрограммы предшествует изменение параметров Microsoft Excel, связанных с вычислением формул: выбираются вычисления в книге «вручную» и включаются итеративные вычисления с предельным числом итераций, равным единице. Кроме того, в ячейку u (G2), управляющую работой ГТИ, заносится единица. Занесение исходных данных в регистр БР осуществляется из РД при выполнении микрокоманды, содержащей в операционной части следующие коды полей: a = 001, w = 1, b – номер регистра БР, в который записываются данные. Данные в РД предварительно вводятся с клавиатуры. Отладка микропрограммы производится путем последовательного выполнения МК по всем возможным ветвям. Выполнение очередной МК инициируется нажатием клавиши F9. Результаты выполнения МК отображаются на экранной форме МПВУ. Обнаруженные в МК ошибки исправляются путем редактирования содержимого БПМП.

Шаги 4 и 5 относятся к экспериментальным исследованиям. В табл. 4 приведен пример выполнения микропрограммы по тактам для случая, когда делимое X = 00000111, а делитель Y = 000000101.

Выполнение микропрограммы завершается в 12 такте после повторного выполнения МК 8 (микрокоманды, записанной в БПМП в ячейке с адресом 1000), когда при очередном вычитании делителя из делимого получается отрицательный результат.

Предложенная функциональная модель МПВУ ориентирована на изучение основ построения, работы и микропрограммирования вычислительных устройств. В то же время наглядное представление структуры устройства на экранной форме и отображение изменений состояний регистров и выходов комбинационных схем в каждом такте делает перспективным применение функциональной модели МПВУ для демонстрации работы устройства при проведении лекционных занятий по изучению вычислительных устройств.

Можно выделить следующие направления развития данной модели:

– усложнение моделируемой вычислительной структуры (подключение к МПВУ запоминающего устройства для хранения исходных данных и результатов, организация перехода к микропрограмме операции по коду операции, введение обращений к подмикропрограммам);

– совершенствование функциональной модели МПВУ как объекта демонстрации (применение в экранной форме цвета, звука, динамического выделения участвующих в выполнении микрокоманд узлов и связей);

– применение при реализации логических функций, описывающих работу узлов и блоков МПВУ, более сложных функций Microsoft Excel, например, логической функции «ПЕРЕКЛЮЧ»; создание и применение пользовательских функций для моделирования работы типовых узлов.

Таблица 4

Выполнение микропрограммы деления чисел нацело в режиме «Такт»

|

T |

МК |

v |

D |

U |

A |

a |

b |

f |

c0 |

w |

s |

z |

p |

Пояснение |

|

РД: = 00000111 |

||||||||||||||

|

1 |

1 |

0 |

0000 |

0 |

00 |

001 |

001 |

000 |

0 |

1 |

0 |

0 |

0 |

R[1]: = РД (R[1] = 00000111) |

|

РД: = 00000101 |

||||||||||||||

|

2 |

2 |

0 |

0000 |

0 |

00 |

001 |

010 |

000 |

0 |

1 |

0 |

0 |

0 |

R[2]: = РД (R[2] = 00000101) |

|

3 |

3 |

0 |

0000 |

0 |

00 |

000 |

011 |

000 |

0 |

1 |

0 |

0 |

0 |

R[3]: = 00000000 |

|

4 |

4 |

0 |

1100 |

0 |

10 |

010 |

000 |

000 |

0 |

0 |

0 |

0 |

0 |

РБ: = R[2] (РБ = 00000101, z = 0) |

|

5 |

5 |

0 |

0000 |

0 |

00 |

000 |

100 |

000 |

0 |

1 |

0 |

0 |

0 |

R[4]: = 00000000 |

|

6 |

6 |

0 |

1101 |

0 |

10 |

001 |

000 |

000 |

0 |

0 |

0 |

0 |

0 |

РБ: = R[1] (РБ = 00000111, z = 0) |

|

7 |

7 |

0 |

0000 |

0 |

00 |

010 |

000 |

000 |

0 |

1 |

0 |

0 |

0 |

R[0]: = РБ (R[0] = 00000111) |

|

8 |

8 |

0 |

1101 |

0 |

11 |

000 |

010 |

111 |

0 |

0 |

0 |

0 |

0 |

РБ: = R[0]-R[2] (РБ = 00000010, p = 0) |

|

9 |

9 |

0 |

0000 |

0 |

00 |

010 |

000 |

000 |

0 |

1 |

0 |

0 |

0 |

R[0]: = РБ (R[0] = 00000010) |

|

10 |

10 |

0 |

0000 |

0 |

00 |

011 |

100 |

110 |

1 |

0 |

0 |

0 |

0 |

РБ: = R[3]+1 (БР = 00000001) |

|

11 |

11 |

0 |

1000 |

1 |

00 |

010 |

011 |

000 |

0 |

1 |

0 |

0 |

0 |

R[3]: = РБ (R[3] = 00000001) |

|

12 |

8 |

0 |

1101 |

0 |

11 |

000 |

010 |

111 |

0 |

0 |

1 |

0 |

1 |

РБ: = R[0]-R[2] (РБ = 11111101, p = 1) |

|

13 |

13 |

1 |

0000 |

0 |

0 |

000 |

000 |

000 |

0 |

0 |

0 |

0 |

0 |

КОНЕЦ |

Заключение

Учебная задача построения функциональной модели МПВУ может оказаться достаточно сложной для обучающихся, поэтому ее решение целесообразно разделить на три подзадачи: разработку модели операционной части, разработку модели управляющей части и объединение построенных моделей в общую модель МПВУ. В процессе комплексной отладки функциональной модели МПВУ проверяется корректность выполнения всех микроопераций в БАЛ и БР, а также порядок формирования адреса следующей МК для всех сочетаний значений логических условий и при безусловных переходах. Индивидуальные задания обучающимся по построению функциональной модели МПВУ могут отличаться наборами микроопераций и логических условий, форматами МК и способами формирования адреса следующей МК.

Учебная задача микропрограммной реализации определенной операции с использованием готовой функциональной модели МПВУ при соответствующей подготовке обучающихся не вызывает у них значительных затруднений и позволяет более глубоко изучить структуру и функционирование по тактам достаточно сложного вычислительного устройства. Составление индивидуальных заданий обучающимся по реализации операции в МПВУ упрощается благодаря большому числу известных простых арифметических преобразований, выполняемых в вычислительных устройствах.

Библиографическая ссылка

Страбыкин Д.А. ФУНКЦИОНАЛЬНАЯ МОДЕЛЬ МИКРОПРОГРАММИРУЕМОГО ВЫЧИСЛИТЕЛЬНОГО УСТРОЙСТВА В MICROSOFT EXCEL ДЛЯ ВЫПОЛНЕНИЯ УЧЕБНЫХ МИКРОПРОГРАММ // Современные наукоемкие технологии. 2022. № 2. С. 121-129;URL: https://top-technologies.ru/ru/article/view?id=39046 (дата обращения: 07.05.2026).

DOI: https://doi.org/10.17513/snt.39046