Сложность и степень интеграции больших интегральных схем (БИС) растет с каждым годом. Наиболее приоритетными и сложным в разработке в настоящее время являются специализированные микросхемы для датчиков различного назначения [1] и интеллектуальных сенсоров, в частности используемых в робототехнике [2]. На настоящий момент развитие технологий по созданию таких «органов чувств» для цифровых систем является важным направлением в микроэлектронике. Такие сенсоры востребованы во многих отраслях, в том числе в медицине (глюкометры, устройства для помощи астматикам, датчики исследования функции сердца), в различных исследованиях (космические исследования, исследования в расщелинах и впадинах Мирового океана), в обеспечении безопасности (датчики радиации, дальномеры, фотобарьеры, портативные средства обнаружения оружия, взрывчатых веществ, датчики для автопилотирования, компьютерное зрение, обработка видео и изображений, видеонаблюдение), автомобилестроение (адаптивное торможение, помощь при парковке, мониторинг препятствий и людей на пути следования транспортного средства, системы автопилотажа) и многие другие [3].

Таким образом, в настоящее время одним из приоритетных направлений в изготовлении отечественных БИС является совершенствование средств автоматизированного проектирования (САПР). Одним из факторов совершенствования считается улучшение подсистем тестирования и отладки.

По данным сайта tadviser.ru, на настоящий момент на рынке САПР присутствует в основном зарубежное программное обеспечение (ПО) от таких крупных компаний, как Autodesk, Dassault Systemes, Siemens PLM Software и других. Обращаясь к российскому рынку, многие отечественные САПР на данный момент не могут в полной мере удовлетворить все потребности в сфере разработки БИС. В качестве примера наиболее полной и доступной отечественной САПР, включающей в себя основные подсистемы проектирования современных БИС, можно привести САПР «Ковчег». В основе САПР «Ковчег» лежит маршрут проектирования БИС от НПК «Технологический центр», характеристика этапов которого рассматривается ниже. Однако отсутствие подсистемы локализации ошибок для этапа логического проектирования заставляет разработчиков обращаться к дорогостоящим зарубежным аналогам, которые могут нести в себе скрытый программный функционал, обеспечивающий внедрение вредоносной аппаратной логики или утечку информации о разрабатываемых проектах. В связи с этим чаще всего обращаются к наиболее подходящему для разработки интегральных микросхем ПО компаний Cadence, Synopsys, Aldec или Xilinx.

Таким образом, одной из проблем является отсутствие российских аналогов ПО для локализации ошибок на этапе функционально-логического моделирования (ФЛМ). Кроме того, отсутствие подсистемы локализации ошибок и исключение возможности применения зарубежного ПО при создании некоторых специализированных БИС особого назначения значительно усложняет и замедляет процесс вывода микросхемы на рынок. Еще одной проблемой, безусловно связанной с первой, является (в связи с вынужденностью использования зарубежного ПО) вероятность встраивания в электрическую схему аппаратных закладок, утечки информации и разрабатываемых проектов. В частности, авторы работы [4] описывают скрытный метод внедрения вредоносной логики в микросхему, и как такая атака может работать на практике. В работе доказывается, что после внедрения подобных изменений в микросхему их обнаружить весьма затруднительно.

В связи с возможностью проявления подобных проблем целесообразно разработать собственную методику и построить на ее основе подсистему локализации ошибок в проектах разработки специализированных БИС.

Целью данной статьи является анализ существующих программных методик локализации ошибок в процессе разработки микросхем, а также постановка цели и задачи на последующее исследование.

Характеристика существующего маршрута проектирования

В процессе разработки БИС используется большое количество различных систем проектирования, которые обеспечивают решение широкого спектра разноплановых задач на каждом из этапов проектирования микросхем. В маршрут проектирования микросхем входят следующие этапы, предложенные НПК «Технологический центр»:

– системное проектирование – разработка системной спецификации и требований к БИС, которым должна удовлетворять будущая микросхема;

– функциональное проектирование – на базе поведенческой модели создается RTL-описание (register transfer level – уровень регистровых передач, в разработке интегральных микросхем – описание работы синхронной цифровой схемы) проектируемой микросхемы, а также проводятся его моделирование;

– логическое проектирование – генерируется структурное описание схемы, состоящее из логических вентилей и их соединений – netlist, проводится логический синтез, ФЛМ;

– физическое (топологическое) проектирование – выполняется размещение ячеек на поле БМК (базовый матричный кристалл), синтез топологии с учетом списков цепей, расчет задержек цепей топологии БИС, оценивается устойчивость проекта БИС при различных внешних воздействиях, проводится анализ влияния параметров топологии на правильность функционирования и устойчивость проекта;

– производство БИС;

– тестирование БИС в составе пластины и в составе корпуса;

– квалификационные испытания БИС – испытания на надежность, радиационную стойкость и др.;

– испытания БИС в составе аппаратуры заказчика.

Продолжительность выполнения любого из этапов проектирования для создания даже простых микросхем может занимать от нескольких дней до нескольких месяцев, сопровождаясь на каждом этапе выполнением значительного количества контрольных операций.

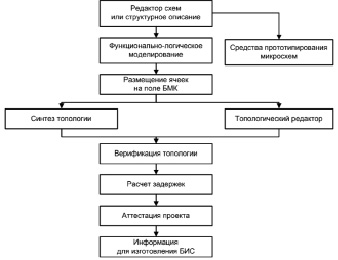

В настоящий момент в рассматриваемый для примера отечественный САПР «Ковчег» входят подсистемы, приведенные на рис. 1.

Рис. 1. Состав САПР «Ковчег» 3.0 [5]

Приведенные на рисунке подсистемы реализуют определенные ранее описанные этапы выведения микросхемы на рынок. Этап системного проектирования реализуется редактором схем со средствами прототипирования микросхем. Этапам функционального и логического проектирования соответствует подсистема функционально-логического моделирования. Подсистемы размещения ячеек на поле БМК, синтеза топологии, верификации, расчета задержек и топологический редактор используются на этапе топологического проектирования. Подсистема аттестации проекта дает возможность оценить устойчивость полученного проекта БИС в зависимости от задаваемых параметров внешних воздействий, проанализировать влияние топологических параметров, оказываемое на правильность функционирования микросхемы. Полученная в ходе разработки микросхемы информация для изготовления БИС передается на последующие этапы производства.

ФЛМ проводится для проверки правильности функционирования микросхемы с учетом задержек функциональных ячеек и проверки на соответствие полученного после логического синтеза netlist и RTL-описания для выявления возможных логических ошибок, то есть проводится формальная верификация.

Анализ методик локализации ошибок в современных САПР

На основе анализа сведений о распространении различных САПР можно сделать вывод, что для разработки интегральных микросхем используются в основном ПО двух крупных фирм – Cadence и Synopsys. Кроме того, используются САПР таких производителей, как Aldec, Xilinx, Altera. В качестве бесплатного САПР рассматривается Icarus. Результаты анализа методик САПР выбранных компаний на основе требований отечественных разработчиков и технологического процесса представлены в таблице.

Характеристика методик поиска ошибок на этапе логического проектирования

|

Методика |

Достоинства методики |

Недостатки методики |

|

Cadence NC-Verilog |

– обширный набор средств и настроек для проверки модели микросхемы; – визуальное отображение схемы; – возможность раскрытия схемы от одного элемента; – возможность просматривать значение сигнала на входах и выходах в процессе моделирования |

– работает под Unix-подобными системами; – освоение системы управления функциями среды занимает большое количество времени |

|

Synopsys VCS |

– возможность отображения информации о микросхеме в разных представлениях (ASCII таблица моделирования и диаграмма сигналов); – визуальное отображение схемы; – возможность отслеживать путь сигнала в схеме БИС в двух режимах – «Path» и «Design» |

– совместимость с Unix-подобными системами; – просмотр только полной схемы без возможности свертки/развертки от элемента; – не содержит в себе всего необходимого спектра функций для сквозного проектирования микросхемы |

|

Aldec Active-HDL |

– возможность внесения изменений и правок в проекте в процессе моделирования и поиска ошибок; – визуальное отображение схемы; – возможность просматривать значение сигнала на входах и выходах элементов схемы в процессе моделирования |

– просмотр только полной схемы без возможности свертки/развертки от элемента |

|

Xilinx ISE |

– возможность внесения изменений и правок в проект в процессе моделирования и поиска ошибок; – возможность отслеживать путь сигнала в схеме микросхемы |

– визуальное отображение схемы без отображения сигнала; – просмотр только полной схемы без возможности свертки от одного элемента |

|

Altera ModelSim |

– возможность внесения изменений и правок в коде проекте в процессе моделирования и поиска ошибок; совместима с Windows |

– все инструкции по работе со средой и сама среда только на английском языке; – просмотр только полной схемы без возможности свертки от одного элемента; – визуальное отображение схемы микросхемы через ПО Altera Quartus II |

|

Icarus Verilog |

– бесплатная версия |

– правки осуществляются разными сторонними программистами, что ставит под угрозу данные проекта; – совместимость с Unix-подобными системами; – полностью отсутствует какое-либо графическое отображение схемы |

Основными требованиями, предъявляемыми к методикам, использованным в рассмотренных САПР, можно считать следующие:

– визуализация – необходима для правильной и более быстрой локализации ошибок в проекте БИС;

– свертка и развертка схемы – требуются для обеспечения возможности убирать с выведенной части схемы ненужные элементы и связи, выводить нужные для анализа элементы во избежание излишней загроможденности на экране;

– удобство просмотра результатов моделирования – необходимо для облегчения визуального поиска ошибок в проекте БИС;

– доступность и дружелюбность ПО по отношению к пользователю;

– операционная система и др.

Анализ проблем защиты данных

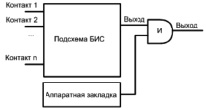

Помимо двух наиболее общих способов внедрения аппаратной вредоносной логики путем внесения модификации на уровне VHDL ((Very high speed integrated circuits) Hardware Description Language) (рисунок), существует еще ряд различных вариантов. Кроме того, что такую закладку зачастую невозможно выявить на этапах разработки и производства, это сложно сделать и в процессе эксплуатации, так как вредоносная закладка может активизироваться не сразу [6].

На рис. 2 представлена схема простейшей аппаратной закладки. В такой схеме реальное значение сигнала на выходе будет получаться при неактивной закладке. В противном случае на выход микросхемы всегда будет поступать «ноль». Активация закладки может осуществляться разными способами, например существуют образцы с внутренней и внешней активацией. Такие закладки активизируются при достижении определенных внутренних состояний или взаимодействуя с каким-либо источником во внешней среде. Такими источниками могут, например, являться антенны внешнего сигнала.

Рис. 2. Пример простейшей аппаратной закладки

В настоящее время не существует единого общего метода или комплекса методов обнаружения аппаратных закладок всех типов. Самым эффективным остается тщательный контроль всего цикла выведения микросхемы на рынок, а также использование собственных или проверенных САПР [7]. Кроме того, требуется детально проверять библиотеки элементов, используемых в основе разработки.

Помимо встраиваемой логики, существует угроза и со стороны программной части, то есть содержания самих зарубежных САПР, особенно при использовании в режиме реального времени через интернет. При открытии проектов микросхем в программной среде может происходить утечка важных частей кода, тестов и другой информации.

Данная проблема в настоящее время также решается использованием проверенного ПО или собственных разработок.

Направления последующего исследования

В настоящее время в России возрастает заинтересованность в специализированных микросхемах. В связи с этим целесообразно не только разработать надежную и проверенную отечественную методику локализации ошибок функционирования в проектах БИС, но и обеспечить наличие в ней современных, быстродействующих инструментов для снижения трудозатрат отечественных разработчиков и уменьшения времени процесса вывода микросхем на рынок.

В рамках достижения поставленных целей необходимо решить следующие задачи.

1. Проанализировать существующие методики локализации ошибок функционирования в микросхемах и алгоритмы различных вспомогательных инструментов с целью выявления наиболее затратных по времени и трудоемких.

2. Разработать методику и реализующие ее алгоритмы локализации ошибок функционирования в проекте БИС для снижения ресурсоемкости этапа логического проектирования.

3. Обосновать преимущество новой методики по сравнению с используемыми.

Выводы

1. На основании анализа преимуществ и недостатков применяемых в настоящее время методик локализации ошибок следует признать, что наиболее совершенным пока является зарубежное ПО производства Cadence и Synopsys.

2. В ходе анализа выявлено отсутствие единого метода выявления различных аппаратных закладок. Из этого следует необходимость создания унифицированного и наиболее полного инструмента для выявления закладок.

3. Сформулированы цели и задачи на последующее исследование, направленное на совершенствование методики локализации ошибок функционирования БИС.

Библиографическая ссылка

Черников Б.В., Можжухина А.В., Борисова Е.А. ПРОБЛЕМЫ ЛОКАЛИЗАЦИИ ОШИБОК ПРИ ПРОЕКТИРОВАНИИ СПЕЦИАЛИЗИРОВАННЫХ БИС // Современные наукоемкие технологии. 2019. № 11-2. С. 301-305;URL: https://top-technologies.ru/ru/article/view?id=37808 (дата обращения: 23.03.2026).

DOI: https://doi.org/10.17513/snt.37808