Введение

Многие образовательные программы высшего и среднего профессионального образования включают дисциплины, имеющие разделы по запоминающим и вычислительным устройствам. Изучение этих устройств, как правило, предполагает выполнение экспериментальных исследований, при проведении которых широко используются имитационные программные модели устройств. Характер экспериментальных исследований в значительной степени зависит от задач обучения. Если при обучении делается акцент на проектировании устройств, то применяются системы автоматизированного проектирования, в состав которых входят необходимые подсистемы моделирования, например [1–3]. В тех случаях, когда экспериментальные исследования проводятся для обеспечения более глубокого изучения структуры и функционирования устройств, ограничиваются применением менее трудоемких в освоении программных средств [4–6]. Большой интерес при углубленном изучении устройств представляют уже готовые симуляторы [7–9].

Цель исследования – развитие технологии построения и применения в учебном процессе функциональных моделей запоминающих и вычислительных структур, состоящих из параллельно работающих узлов и блоков, позволяющей создавать и экспериментально исследовать с помощью Microsoft Excel модели регистровых безадресных запоминающих (ЗУ) устройств со сдвигом информации типа стек и очередь.

Материалы и методы исследования

У безадресных ЗУ нет входов для указания адреса ячейки. В ЗУ типа стек запись и считывание производится через один и тот же вход-выход данных (запись данных осуществляется в порядке поступления, а чтение – в обратном порядке) [10, 11]. В ЗУ типа очередь запись производится в порядке их поступления через один вход, а считывание – через один выход данных [12–14]. Известно несколько подходов к построению безадресных ЗУ, которые можно разделить на два основных типа: 1) регистровые структуры со сдвигом информации; 2) устройства на основе блока памяти со сдвигом адресного маркера [15]. В статье приводится разработка функциональной модели стека и очереди на основе блока регистров со сдвигом информации, в котором хранящиеся в ячейках памяти данные могут одновременно перемещаться в соседние ячейки. Создание модели ЗУ включает: выбор структуры и режимов работы; разработку экранной формы для экспериментального исследования, описание функционирования с помощью таблиц переходов; представление описания функционирования в виде формул Microsoft Excel.

Результаты исследования и их обсуждение

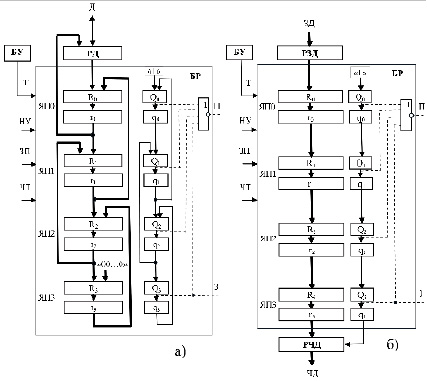

Структура и режимы работы моделируемого стека и очереди. Структура моделируемого стека приведена на рис. 1, а, где РД – регистр данных; БР – блок регистров, содержащий ячейки памяти ЯПi (i = 0, 1, 2, 3), каждая из которых состоит из пары регистров Ri и ri, а также пары триггеров Qi и qi для признаков наличия данных в соответствующих регистрах (при единичном состоянии триггера регистр занят, иначе свободен); П и З – осведомительные сигналы (если П = 1, то стек пуст, а если З = 1 – полностью заполнен). В состав стека также входит блок управления (БУ), вырабатывающий тактовые сигналы (Т). Кроме тактовых сигналов во все регистры и триггеры стека подаются управляющие сигналы: НУ – начальной установки (все регистры и триггеры устанавливаются в нулевое состояние), ЗП – записи (содержимое РД записывается в верхнюю ЯП стека), ЧТ – чтения (в РД считывается содержимое верхней ЯП стека).

Стек работает в трех режимах: запись, чтение и хранение. Запись производится при З = 0 по сигналу ЗП за два такта. В первом такте (T = 1) одновременно выполняются следующие микрооперации: R0: = РД; R1: = r0; R2: = r1; R3: = r2; Q0: = 1; Q1: = q0; Q2: = q1; Q3: = q2; а во втором (T = 0) – r0: = R0; r1: = R1, r2: = R2 r3: = R2; q0: = Q0; q1: = Q1; q2: = Q2; q3: = Q3. Чтение осуществляется при П = 0 по сигналу ЧТ также за два такта. В первом такте (T = 1) одновременно выполняются следующие микрооперации: РД: = r0; R0: = r1; R1: = r2; R2: = r3; R3: = 00…0; Q0: = q1; Q1: = q2; Q2: = q3; Q3: = 0; а во втором (T = 0) – r0: = R0; r1: = R1, r2: = R2 r3: = R2; q0: = Q0; q1: = Q1; q2: = Q2; q3: = Q3. При отсутствии сигналов ЗП и ЧТ стек находится в режиме хранения. Осведомительные сигналы формируются в соответствии со следующими формулами: З = Q3; П = (Q0∨Q1∨ Q2∨Q3).

Структура рассматриваемой очереди во многом совпадет со структурой стека. Основное отличие заключается в том, что в очереди отсутствуют связи между ЯП, обеспечивающие передачу данных в обратном направлении, а также используется два регистра: РЗД – регистр записываемых данных и РЧД – регистр читаемых данных (рис. 1, б). Очередь работает также в трех режимах: запись, чтение и хранение. Работа очереди отличается от работы стека в режимах записи и чтения. В процессе записи при З = 0 в первом такте (T = 1) одновременно выполняются микрооперации: R0: = РЗД; R1: = r0; R2: = r1; R3: = r2; Q0: = 1; Q1: = q0; Q2: = q1; Q3: = q2. В процессе чтения при П = 0 в первом такте (T = 1) одновременно выполняются микрооперации: R0: = 00…0; R1: = r0; R2: = r1; R3: = r2; РЧД: = r3; Q0: = 0; Q1: = q0; Q2: = q1; Q3: = q2.

Работа приведенной на рис. 1, б, очереди имеет две особенности: чтение записанного данного возможно только после того, как оно достигнет головы очереди (очередь полностью заполнится); запись новых данных в освободившиеся после чтения ячейки (если очередь не пуста) без потери ранее записанных данных невозможна. Далее разрабатывается модель усовершенствованного варианта очереди, в которой данные могут записываться в освободившиеся после чтения ячейки.

Рис. 1. Стек (а) и очередь (б) на основе блока регистров Источник: составлено автором по результатам данного исследования

Моделируемая очередь отличается организацией записи, которая использует специальный признак zi (i = 0, 1, 2, 3) возможности записи в i-ю ЯП. Признак zi определяет наличие после i-й ЯП свободной ячейки памяти. Свободная ЯП позволяет произвести сдвиг содержимого только группы ячеек, начиная с головы очереди до свободной ЯП. При этом занимается первая свободная ЯП, а в голову очереди записывается новое данное. Признаки возможности записи вычисляются следующим образом: z0 = (Q0&Q1&Q2&Q3), z1 = (Q1&Q2&Q3), z2 = (Q2&Q3), z3 = Q3. Структура моделируемой очереди отличается от структуры ранее рассмотренной введением дополнительных схем, формирующих признаки возможности записи zi (i = 0, 1, 2, 3) в соответствии с приведенными выше формулами, и модификацией схемы признака полного заполнения очереди, который вычисляется в соответствии с формулой З = Q0&Q1&Q2&Q3 (З = z0). Отличия в работе моделируемой очереди проявляются в том, в процессе записи (при З = 0) в первом такте (T = 1) одновременно выполняются микрооперации: R0: = РЗД и Q0: = 1; при z1 = 1 R1: = r0; и Q1: = q0; при z2 = 1 R2: = r1 и Q2: = q1; при z3 = 1 R3: = r2 и Q3: = q2.

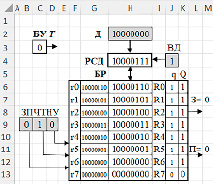

Разработка функциональных моделей стека и очереди. Функциональная модель учебного варианта стека разрабатывается на основе блока регистров, содержащего 8 восьмиразрядных ячеек памяти (ЯП i, i = 0,1,…,7), каждая из которых состоит из пары регистров Ri и ri, а также пары триггеров Qi и qi. Структура учебного стека при проведении экспериментальных исследований отображается на экранной форме (рис. 2, а), где ВД – управляющий сигнал ввода данных, Д – поле ввода данных, РСД – регистр-счетчик данных, позволяющий в режиме записи (при ВД = 1) увеличивать содержимое РСД на единицу.

а) б)

Рис. 2. Экранная форма для стека (а) и очереди (б) Источник: составлено автором по результатам данного исследования

Таблица 1

Изменение состояний РСД, регистров накопителя стека (R и r), триггеров (Q и q)

|

Регистр / триггер |

НУ = 1 |

ЗП = 1 (НУ = ЧТ = 0; З = 0) |

ЧТ = 1 (НУ = ЗП = 0; П = 0) |

||

|

Т = 0 |

Т = 0 |

Т = 1 |

Т = 0 |

Т = 1 |

|

|

РСД |

= Д |

= Д, при ВД = 0; = РСД+1, при ВД = 1 |

– |

– |

= r0 |

|

Ri |

= 00000000, i = 0,1,…,7 |

– |

= ri-1, i = 1,2,…7; R0 = РСД |

– |

= ri+1, i = 0,1,…,6; R7 = 000000000 |

|

ri |

= 00000000, i = 0,1,…,7 |

= Ri; i = 0,1,…,7 |

– |

= Ri; i = 0,1,…,7 |

– |

|

Qi |

= 0, i = 0,1,…,7 |

– |

= qi-1, i = 1,2,…,7; Q0 = 1 |

– |

= qi+1, i = 0,1,…,6; Q7 = 0 |

|

qi |

= 0, i = 0,1,…,7 |

= Qi; i = 0,1,…,7 |

– |

= Qi; i = 0,1,…,7 |

– |

Источник: составлено автором на основе полученных данных в ходе исследования.

Таблица 2

Изменение состояний РСД, РЧД, регистров накопителя очереди (R), триггеров (Q)

|

Регистр /триггер |

НУ = 1 |

ЗП = 1 (НУ = ЧТ = 0; З = 0) |

ЧТ = 1 (НУ = ЗП = 0; П = 0) |

||

|

Т = 0 |

Т = 0 |

Т = 1 |

Т = 0 |

Т = 1 |

|

|

РСД |

= Д |

= Д, при ВД = 0; = РСД+1, при ВД = 1 |

– |

– |

– |

|

Ri |

= 00000000, i = 0,1,…,7 |

– |

= ri-1, i = 1,2,…7; если zi = 1, иначе Ri R0 = РСД, если z0 = 1, иначе R0 |

– |

= ri-1, i = 1,2,…7; R0 = 000000000 |

|

Qi |

= 0, i = 0,1,…,7 |

– |

= qi-1, i = 1,2,…,7; если zi = 1, иначе Qi Q0 = 1, если z0 = 1, иначе Q0 |

– |

= qi-1, i = 1,2,…,7; Q0 = 0 |

|

РЧД |

= 00000000 |

– |

– |

_ |

= r7 при q7 = 1; = РЧД при q7 = 0 |

Источник: составлено автором на основе полученных данных в ходе исследования.

Функционирование стека описывается изменениями состояний РСД, регистров накопителя стека Ri и ri (i = 0,1,…,7), триггеров Qi и qi (i = 0,1,…,7) в соответствии с управляющими и тактовыми сигналами с помощью таблицы переходов (табл. 1).

При ЗП = ЧТ стек находится в режиме хранения. Осведомительные сигналы полностью заполненного и пустого стека формируются в соответствии со следующими формулами: З = Q7; П = (Q0∨Q1∨…∨Q7).

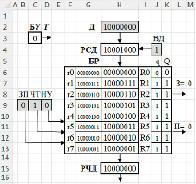

Функциональная модель учебного варианта очереди, как и стека, разрабатывается на основе блока регистров, содержащего 8 восьмиразрядных ячеек памяти (ЯП i, i = 0,1,…,7), каждая из которых состоит из пары регистров Ri и ri, а также пары триггеров Qi и qi. Для удобства проведения экспериментальных исследований функциональная модель очереди, так же как и модель учебного варианта стека, содержит поля управляющих сигналов и поле данных, а вместо регистра записи данных используется регистр-счетчик данных (РСД). Структура учебной очереди при проведении экспериментальных исследований отображается на экранной форме, приведенной на рис. 2, б. Функционирование очереди описывается таблицей переходов (табл. 2).

Описания изменений состояний регистров ri (i = 0,1,…,7) и триггеров ri (i = 0,1,…,7) очереди совпадают с описаниями в таблице переходов стека (табл. 1). Внутренние признаки возможности записи zi вычисляются по формулам zi = (Qi&…&Q7), i = 0,1,…,7. Осведомительные сигналы полностью заполненной и пустой очереди формируются в соответствии со следующими формулами: З = Q0&Q1&…&Q7; П = (Q0∨Q1∨…∨Q7). При ЗП = ЧТ очередь находится в режиме хранения.

Реализация функций стека и очереди с помощью функций Microsoft Excel. В процессе разработки функциональных моделей использовался подход, основанный на пословном моделировании основных узлов и блоков ЭВМ с помощью стандартных функций Microsoft Excel, когда в ячейках могут находиться многоразрядные двоичные коды, а вычисления производятся в десятичной системе счисления. При этом сохраняется представление состояний входов и выходов узлов и блоков на экранных формах в двоичной системе счисления, а для моделирования функционирования последовательностных схем используются формулы с циклическими ссылками [11].

В процессе разработки функциональной модели стека использовались следующие основные функции Microsoft Excel: НЕ, И, ИЛИ, ИСКЛИЛИ, ЕСЛИ, ОСНОВАНИЕ и ДЕС.

Таблица 3

Функциональное моделирование узлов и блоков стека

|

Узел/блок |

Формула Microsoft Excel |

|

БУ(T)[С3] |

= ЕСЛИ(И(НЕ(НУ);ИСКЛИЛИ(ЗП;ЧТ);НЕ(Т));1;0) |

|

РСД[H4] |

= ЕСЛИ(НУ;Д;ЕСЛИ(И(ВД = 0;ЗП;Т = 0);Д;ЕСЛИ(Т = 0;ЕСЛИ(И(ЗП;ВД = 1;НЕ(ЧТ));ОСНОВАНИЕ(ДЕС(РСД;2)+1;2;8);ЕСЛИ(И(ЧТ;НЕ(ЗП));G6;РСД));РСД))) |

|

R0[H6] |

= ЕСЛИ(НУ;»00000000»;ЕСЛИ(Т;ЕСЛИ(И(ЗП;НЕ(ЧТ);НЕ(З));РСД;ЕСЛИ(И(ЧТ;НЕ(ЗП);НЕ(П));G7;H6));H6)) |

|

R1[H7] |

= ЕСЛИ(НУ;»00000000»;ЕСЛИ(Т;ЕСЛИ(И(ЗП;НЕ(ЧТ);НЕ(З));G6;ЕСЛИ(И(ЧТ;НЕ(ЗП);НЕ(П));G8;H7));H7)) |

|

R7[H13] |

= ЕСЛИ(НУ;»00000000»;ЕСЛИ(Т;ЕСЛИ(И(ЗП;НЕ(ЧТ);НЕ(З));G12;ЕСЛИ(И(ЧТ;НЕ(ЗП);НЕ(П));»00000000»;H13));H13)) |

|

r0[G6] |

= ЕСЛИ(НУ;»00000000»;ЕСЛИ(И(Т;ИЛИ(ЗП;ЧТ));G6;H6)) |

|

Q0[K6] |

= ЕСЛИ(НУ;0;ЕСЛИ(Т;ЕСЛИ(И(ЗП;НЕ(ЧТ);НЕ(З));1;ЕСЛИ(И(ЧТ;НЕ(ЗП);НЕ(П));J7;K6));K6)) |

|

Q1[K7] |

= ЕСЛИ(НУ;0;ЕСЛИ(Т;ЕСЛИ(И(ЗП;НЕ(ЧТ);НЕ(З));J6;ЕСЛИ(И(ЧТ;НЕ(ЗП);НЕ(П));J8;K7));K7)) |

|

Q7[K13] |

= ЕСЛИ(НУ;0;ЕСЛИ(Т;ЕСЛИ(И(ЗП;НЕ(ЧТ);НЕ(З));J12;ЕСЛИ(И(ЧТ;НЕ(ЗП);НЕ(П));0;K13));K13)) |

|

q0[J6] |

= ЕСЛИ(НУ;0;ЕСЛИ(И(Т;ИЛИ(ЗП;ЧТ));J6;K6)) |

|

З[M7] |

= ЕСЛИ(K13;1;0) |

|

П[M11] |

= ЕСЛИ(ИЛИ(K6:K13);0;1) |

Источник: составлено автором на основе полученных данных в ходе исследования.

Таблица 4

Функциональное моделирование узлов и блоков очереди

|

Узел/блок |

Формула Microsoft Excel |

|

РСД[H4] |

= ЕСЛИ(НУ;Д;ЕСЛИ(И(НЕ(Т);ЗП;ВД = 0);Д;ЕСЛИ(И(НЕ(Т);ЗП;ВД = 1;НЕ(ЧТ));ОСНОВАНИЕ(ДЕС(РСД;2)+1;2;8);РСД))) |

|

R0[H6] |

= ЕСЛИ(НУ;»00000000»;ЕСЛИ(Т;ЕСЛИ(И(ЗП;НЕ(ЧТ);НЕ(И(K6:K13)));РСД;ЕСЛИ(И(ЧТ;НЕ(ЗП);НЕ(П));»00000000»;H6));H6)) |

|

R1[H7] |

= ЕСЛИ(НУ;»00000000»;ЕСЛИ(Т;ЕСЛИ(ИЛИ(И(ЗП;НЕ(ЧТ);НЕ(И(K7:K13)));И(ЧТ;НЕ(ЗП);НЕ(П)));G6;H7);H7)) |

|

R7[H13] |

= ЕСЛИ(НУ;»00000000»;ЕСЛИ(Т;ЕСЛИ(ИЛИ(И(ЗП;НЕ(ЧТ);НЕ(K13));И(ЧТ;НЕ(ЗП);НЕ(П)));G12;H13);H13)) |

|

Q0[K6] |

= ЕСЛИ(НУ;0;ЕСЛИ(Т;ЕСЛИ(И(ЗП;НЕ(ЧТ);НЕ(И(K6:K13)));1;ЕСЛИ(И(ЧТ;НЕ(ЗП);НЕ(П));0;K6));K6)) |

|

Q1[K7] |

= ЕСЛИ(НУ;0;ЕСЛИ(Т;ЕСЛИ(ИЛИ(И(ЗП;НЕ(ЧТ);НЕ(И(K7:K13)));И(ЧТ;НЕ(ЗП);НЕ(П)));J6;K7);K7)) |

|

Q7[K13] |

= ЕСЛИ(НУ;0;ЕСЛИ(Т;ЕСЛИ(ИЛИ(И(ЗП;НЕ(ЧТ);НЕ(K13));И(ЧТ;НЕ(ЗП);НЕ(П)));J12;K13);K13)) |

|

q0[J6] |

= ЕСЛИ(НУ;0;ЕСЛИ(И(Т;ИЛИ(ЗП;ЧТ));J6;K6)) |

|

З[M7] |

= ЕСЛИ(И(K6:K13);1;0) |

|

РЧД[H15] |

= ЕСЛИ(НУ;»00000000»;ЕСЛИ(И(Т;ЧТ;НЕ(ЗП);J13);G13;РЧД)) |

Источник: составлено автором на основе полученных данных в ходе исследования.

Функциональное моделирование узлов и блоков стека осуществляется на основе таблицы переходов (табл. 1) и экранной формы (рис. 2, а) с помощью формул Microsoft Excel. Каждому узлу и блоку выделяется соответствующая ячейка Microsoft Excel, номер которой указывается в квадратных скобах (табл. 3). Для облегчения восприятия формул, большей части используемых в них ссылок на ячейки присвоены имена, совпадающие с раннее принятыми обозначениями сигналов и состояний входов и выходов моделируемых узлов и блоков. Поскольку формулы для регистров R1–R6 однотипны, приводится формула только R1[H7]. Аналогично формулы для всех регистров r0–r7 иллюстрирует формула r0[G6].

В процессе разработки функциональной модели очереди использовались те же функции Microsoft Excel, что и при разработке модели стека. Описание функциональной модели очереди приведено в табл. 4, в которую не включены формулы, совпадающие с формулами в табл. 3 (БУ(T)[С3], r0[G6], q0[J6], П[M11].

Экспериментальные исследования устройств заключаются в выполнении по тактам заданных последовательностей операций, состоящих из записи и чтения данных, включая последовательности, приводящие к полному заполнению и полному освобождению накопителя моделируемого устройства. При этом в Microsoft Excel включаются итеративные вычисления с предельным числом итераций равным единице. Компактность разработанных экранных форм дает возможность помещать их на одном листе Microsoft Excel и наблюдать параллельную работу моделей двух устройств. Наглядное представление одновременной работы устройств при выполнении одной и той же последовательности операций, состоящей из записи и чтения данных, облегчает понимание обучающимися особенностей функционирования исследуемых устройств.

Заключение

Применение технологии построения и использования в учебном процессе функциональных моделей запоминающих и вычислительных структур для создания моделей регистровых ЗУ со сдвигом информации типа стек и очередь, состоящих из параллельно работающих узлов и блоков, позволяет сделать следующие выводы. Функционирование моделируемого устройства может быть описано с помощью специальной таблицы – таблицы переходов, в которой фиксируются изменения состояний представленных в модели узлов и блоков в процессе их параллельной работы в зависимости от значений управляющих и тактовых сигналов. В таблицах для рассмотренного примера стека и очереди представлено одновременное перемещение хранящихся в ячейках памяти данных в соседние ячейки. При разработке экранной формы, отражающей структуру моделируемого устройства, для каждого моделируемого узла и блока определяется ячейка Microsoft Excel, в которой будет отображаться его состояние. Моделирование функционирования узлов и блоков производится с помощью формул Microsoft Excel на основе таблицы переходов и экранной формы устройства. Для облегчения восприятия формул в них вместо ссылок на ячейки можно использовать имена, совпадающие с привычными обозначениями сигналов и состояний узлов и блоков, введенными при описании моделируемого устройства. Кроме того, Microsoft Excel позволяет установить на листе с экранной формой устройства защиту, которая обеспечит изменение содержимого только ячеек, соответствующих полям ввода данных и управляющих сигналов, и защитит формулы модели от непреднамеренных изменений. Применение технологии построения и использования в учебном процессе функциональных моделей запоминающих и вычислительных структур оказывается полезным при самостоятельной разработке студентами моделей различных устройств, а созданные модели являются перспективным видом демонстрационного материала на лекциях.

Конфликт интересов

Библиографическая ссылка

Страбыкин Д.А. ФУНКЦИОНАЛЬНЫЕ МОДЕЛИ УЧЕБНЫХ РЕГИСТРОВЫХ БЕЗАДРЕСНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ СО СДВИГОМ ИНФОРМАЦИИ // Современные наукоемкие технологии. 2025. № 8. С. 154-160;URL: https://top-technologies.ru/ru/article/view?id=40478 (дата обращения: 06.05.2026).

DOI: https://doi.org/10.17513/snt.40478